Skrivet av Cybertsen:

Men du har påstått att: "I teorin fungerar det" (inlägg #44)

Då är jag lite inne på samma linje som Balls Of Steel: "Upp till bevis!"

Förklara hur kopplar man ihop två processorer i ett single-sockel system?

Och nu snackar vi praktik, inte lite svävande beskrivning om vad ett multiprocessorsystem är eller hur man löste det historiskt.

Eller är det som det som du skriver i ditt nästa inlägg (#46): "Jag tror inte det är omöjligt."

Först säger du alltså att det fungerar, sedan tror du att det inte är omöjligt...men vet du?

Så: "Upp till bevis!"

Skulle vara kul om det fungerade, men då måste du förklara för mig hur det är praktisk möjligt...

Du har rätt. Det är inte praktiskt möjligt, men... det är inte omöjligt.

Jag ville med mitt första inlägg skilja på "omöjligt" och "praktiskt icke genomförbart". För mig är "Omöjligt" ett mycket starkt ord.

Så... till sak:

Försöker mig på en enkel förklaring, men tyvärr har jag inte resurser nog (Tid, Pengar, utrustning) att producera bevis.

En processor, har, enkelt sett:

Adressbuss.

Databuss.

Minnesbuss.

IRQ-signaler.

Strömförsörjning.

Konfigurations-stift.

Ledningar mellan processorerna som kan parallell-kopplas direkt:

Ledningar som bör/måste hanteras av separata stöd-kretsar:

IRQ-signaler.

Konfigurations-stift.

Ledningar som kopplas antigen separat eller parallellt, beroende på tillverkare, generation och andra faktorer.

Minnesbuss.

Strömförsörjning.

Data- och adress- bussar.

Först och främst, data och adressbussarna. Det enda sättet för processorer att kunna dela data med resten av systemet, och mellan varandra, är via adress och databussen. Kort och kott är dessa bussar enbart en bunt ledningar som parallell-kopplas mellan samtliga inblandade enheter i ett system. Inte bara processorerna.

Är systemet ett 32-bitars system, med 32 bitars adressering, är det 64 ledningar att parallell-koppla mellan samtliga enheter, inklusive processorer.

Till detta tillkommer avskärmningsledningar, termineringar och annat tillverkar-specifikt, men det går vi inte in på här.

IRQ

Sedan kommer ledningarna/signalerna som inte kan parallell-kopplas, och måste hanteras individuellt. IRQ är en av dessa signaler som måste hanteras separat. IRQ 0 är i regel kopplad till master-processorn. Därefter tillkommer en bunt ytterligare IRQ-signaler, alla via en egen ledning, som ansluts till individuellt hårdvara. (Förr i tiden var det jumprar som skötte IRQ-signalerna, och det var vanligt att orsaka så kallade IRQ-krockar om mer än en enhet var ansluten till samma IRQ-ledning. Ytterligare processorer har sina egna IRQ-signaler, och tilldelas de signaler som är lediga.

I moderna processorer, hanteras alla processorer av IRQ 0, och har ersatts av en mer diskret ID-hantering där master-CPUn bestämmer när andra processorer får svara på anrop (Operativsystemets kärna sköter det).

Strömförsörjning

Förr i tiden var processorer inte så kinkiga, utan drevs av en "råmatning" på 5 volt direkt från nätaggregatet. Det dög gott.

Idag är processorer så extremt kinkiga, and hundradels volt skillnad kan innebära felberäkningar. Därför försörjes varje processor av sin egen dedikerade spänningsregulator.

Hittar man, mot all förmodan, två eller fler processorer som har samma toleranser, kan man ansluta dessa till samma regulator, om regulatorn är stark nog för detta.

Minnesbussen

Nu kommer vill till det intressanta: RAM

Förr i tiden satt RAM-minnet på samma fysiska adress- och data- buss som resten av systemet, vilket gjorde att parallellkoppling av flera processorer var mycket enkelt.

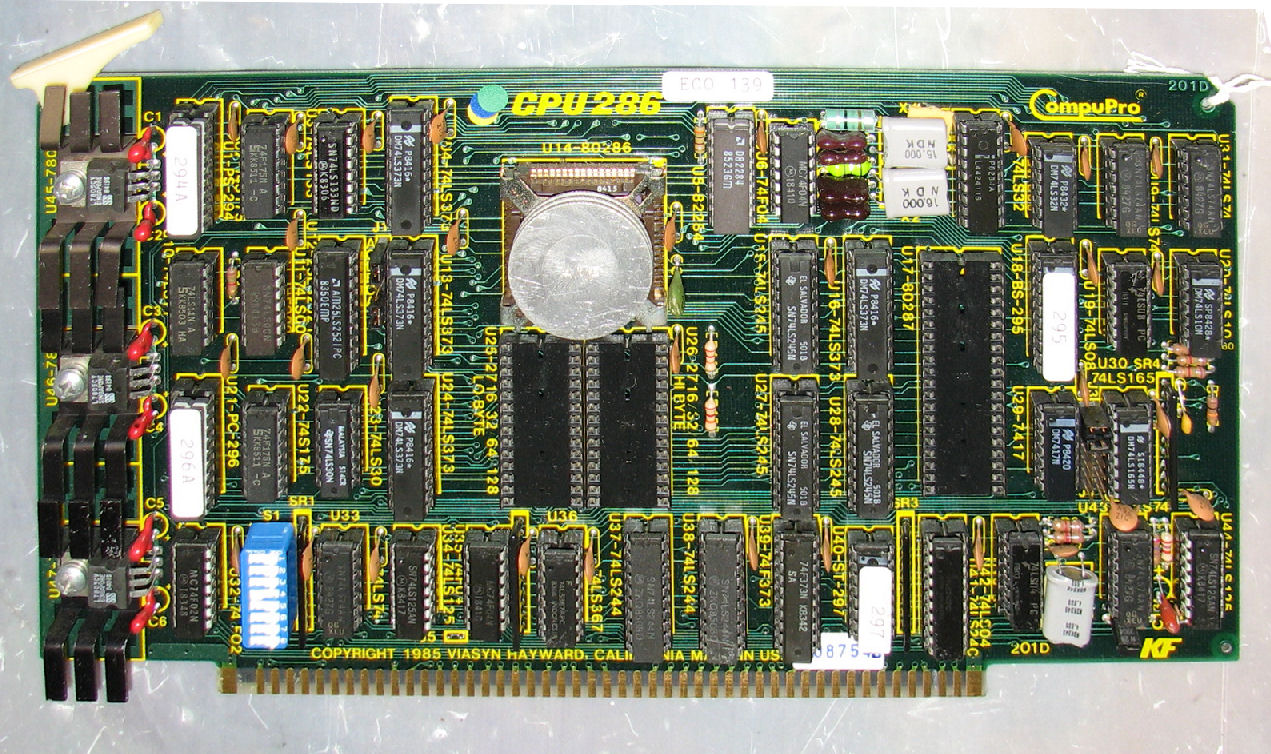

Senare i tiden tillkom en separat stöd-krets för att kunna kommunicera med RAM-minnena, men denna krets var ansluten till den gemensamma data- och adress- bussen. (Samma ledningar, parallellt med resterande enheter).

Då bestod minnesbussen enbart av de korta ledningarna mellan RAM-kapslarna och minneskontrollern.

Idag har minneskontrollern integrerats med processorn, och det ställer till det med parallell-kopplingen av processorerna, då det har tillkommit en ytterligare buss: Minnesbussen.

Tyvärr är dagens minneskretsar inte designade att hantera multipla läsningar och skrivningar samtidigt, så då löser man det genom att ge varje processor sina egna minnes-kapslar. Därför måste ett moderkort som använder 4 fysiska processorer ha minst 4 stycken minneskapslar. En till varje processor.

Kommunikationen mellan varje processors minnesbank sker via den gemensamma data- och adress- bussen.

Det betyder alltså att varje processor då måste fråga en annan processors om informationen. Det slösar bort processortid om en applikation använder mer minne än det som finns tillgängligt hos en aktuella processorn.

För att slippa förslöande minnesförfrågningar mellan processorerna, designades ett speciellt läge som kallas "Memory Ganged Mode". Jag tänker inte gå i i detalj hur detta fungerar. Inlägget skulle bli ännu längre, och det berör inte det aktuella ämnet i alla fall.

Konfigurations-stiften till varje processor.

Varje processor och kärna har sina egna konfigurations-stift anslutna till nordbryggan.

Nordbryggan kommer vid initiering försöka läsa av processorernas serial-ID stift och ladda ner konfigurations-data, eller använda förinställda värden lagrade i CMOS-kretsen. Varje kärna/processor ställs därefter in, så att spänningsmatningen och frekvenser blir dem rätta för varje kärna/processor.

Kort därpå hämtas även minneskapslarnas data in via ytterligare separata ledningar. Detta är dock ett annat ämne vi inte går igenom här.

Uppdatering: I en del moderna system, saknas nordbryggan, då de flesta vitala funktioner från en nordbrygga har flyttat in i processorn.

Detaljer om hur det skulle gå till i dessa vall har jag inte, men generellt sett så måste processorn hämta in/uppdatera sin konfiguration via någon separat stöd-krets, som i sin tur hämtar data från CMOS/EFI.

Låt oss leka med tanken, och låtsas att TS är galen nog att genomföra projektet, har utrustning för SMD-lödning, "reflow"-ugn, och de rätta verktygen:

Denne behöver "bara" parallell-koppla data och adressbussen, ge processorn en egen spännings-regulator, kortsluta rätt konfigurations-stift och knöka in en minneskapsel till processorns minnesbuss.

Här skulle jag rekommendera att man bryter ut alla ledningarna från moderkortet som behövs genom att löda in en så kallad "breakout board" under moderkortet till processorsockelns löd-punkter. Dra så korta ledningar som möjligt.

Anslut den nya processorn till "breakout-kortet", löd in spänningsregulatorer och filterkretsar, anslut strömförsörjning, och anslut en logik-krets till konfigurations-stiften. Det finns även ett stift för seriell konfigurations-data. Denne ansluts till nordbryggan.

Nord-bryggan borde ha lediga konfigurations-ledningar för ytterligare processorer/kärnor.

I bästa fall behöver man bara konfigurera om nordbryggan, så att ytterligare processorer lämnar sina ID-koder och annan data som behövs för operativsystemet skall kunna detektera eventuella extra processorer.

I värsta fall måste nord-bryggan bytas ut mot en som är bättre anpassad för uppgiften i fråga.

Sedan löder TS dit en eller flera minnesslottar på breakout-kortet intill processorn, och drar dess ledningar till processorns minnes-buss.

Resterande...

Resten blir bara lite småpill, smärre anpassningar och trial'n'error.

Självfallet kommer det inte att fungera rakt av, såvida TS inte är en extremt tålmodig människa med "Super-Asian skills"

Slutsats:

Praktiskt genomförbart? Knappast!

Det skulle bli ett mastodont-projekt som skulle ta stora resurser och gräva en krater i ens plånbok.

Omöjligt? Nej.

Parallell-kopplat? Inte allt, men större delen av processorns signaler.

Jag gissar att ni aldrig kommer att läsa dessa rader, då de flesta normala människor har tröttnat en bra bit innan detta, men jag skriver dessa rader ändå:

Vad är syftet med att bevisa det jag beskrev ovan?, vad är det som skall bevisas? vad var det med mitt första inlägg ni missade?

TS fick ju redan svar på sin fråga: Inte praktiskt genomförbart. Det är billigare och enklare att köpa ett moderkort designat för ändamålet.

Jag säger det återigen:

Jag ville med mitt första inlägg skilja på "omöjligt" och "praktiskt icke genomförbart". För mig är "Omöjligt" ett mycket starkt ord.

Istället för att kalla TS "korkad", så som många andra gör, så ville jag med mitt första inlägg beskriva att de inte är omöjligt att parallell-koppla, och att TS delvist är inne på rätt spår, men...

EDIT:

Varför jag skrev det jag skrev, är för att jag uppfattade TS fråga som en teoretisk fråga, och jag gav ett teoretiskt svar.

Jag tror nog att TS själv fattar att det inte är praktiskt genomförbart.