Observera att samma trivselregler gäller i kommentarstrådarna som i övriga forumet och att brott mot dessa kan leda till avstängning. Kontakta redaktionen om du vill uppmärksamma fel i artikeln eller framföra andra synpunkter.

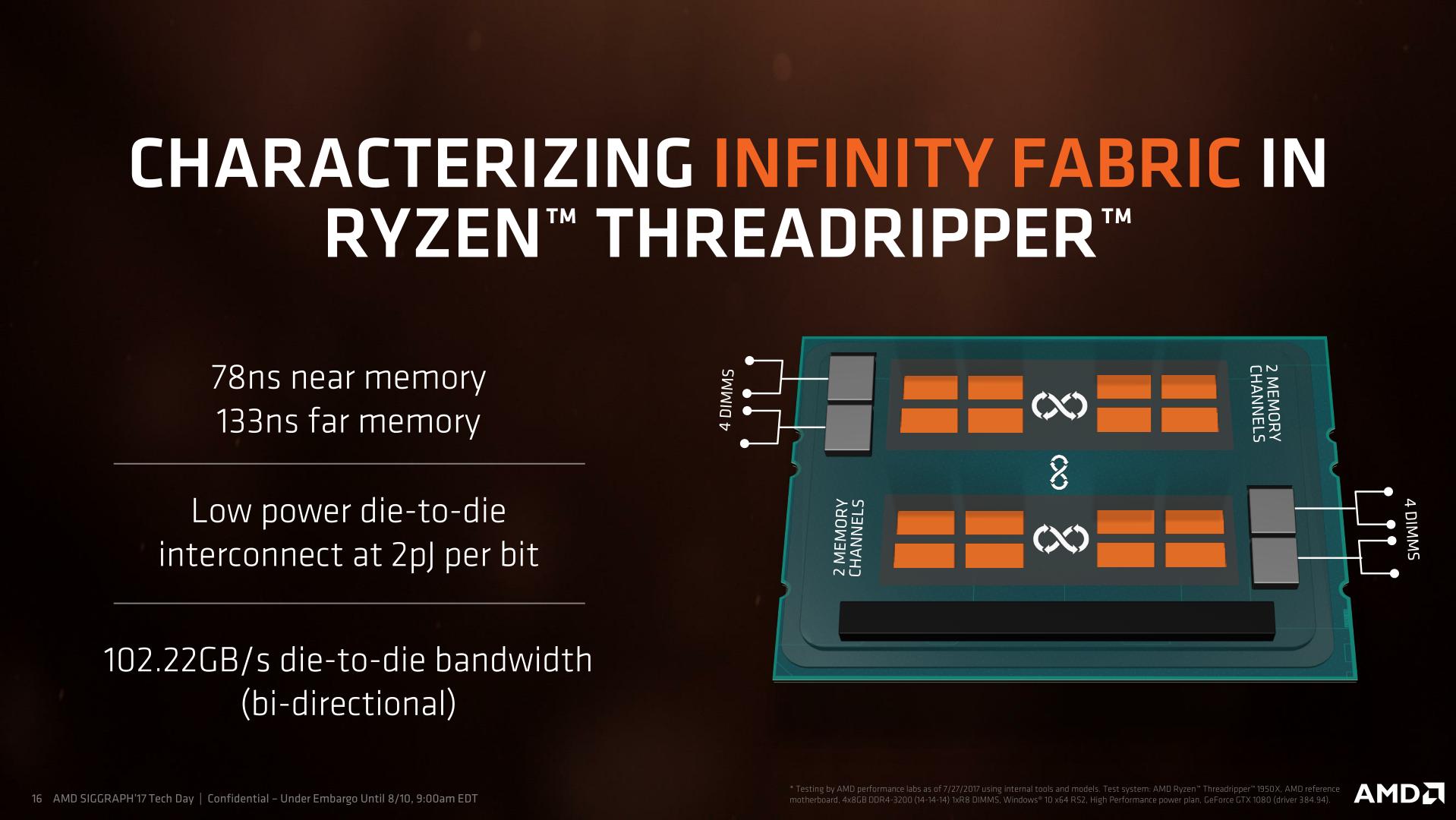

AMD förklarar fyra kretsar hos Ryzen Threadripper

Visa signatur

Visa signatur

Spelburk: R7 5700X | 5700 XT | 32GB RAM | MSI B350M PRO-VDH

Visa signatur

ozzed.net Min egenkomponerade 8-bit musik. Gillar du musiken från gamla klassiska NES eller Gameboy och liknande är det värt ett besök. :) Jag finns också på Spotify, Bandcamp, Jamendo, Youtube, och du kan även följa mig på Twitter och Facebook.

Vet du att du har fel? Signalera detta tydligt med Argumentationsfel och gärna Whataboutism.

Visa signatur

Cooler Master ATCS840 | Cooler Master Silent Pro Gold 1200W | Fractal Design Newton R3 1000W

ASUSTeK Z9PE-D8 WS | 2x Intel Xeon E5-2697 v2 | Kingston 128 GB DDR3 ECC | Gigabyte Geforce GTX 1070 Ti

BOINC : asteroids | einstein | enigma | milkyway | seti | universe | TheSkyNet POGS

Visa signatur

12900K, 48GB DDR5, GTX Titan Xp 12GB

Senast redigerat

Visa signatur

Assembly är ett högnivåspråk.

Visa signatur

PC #1 CPU: R5 1600 @3.8 Motherboard: B350-A PRIME GPU: EVGA 1080 Ti

PC #2 CPU: i7 3770K @4.2 Motherboard: P8P67 GPU: AMD R9 290X

Visa signatur

PC #1 CPU: R5 1600 @3.8 Motherboard: B350-A PRIME GPU: EVGA 1080 Ti

PC #2 CPU: i7 3770K @4.2 Motherboard: P8P67 GPU: AMD R9 290X

Visa signatur

12900K, 48GB DDR5, GTX Titan Xp 12GB

Visa signatur

Care About Your Craft: Why spend your life developing software unless you care about doing it well? - The Pragmatic Programmer

Visa signatur

Main: 5800X3D | Arctic Freezer III 360 | ROG STRIX B550-I | 32 GB DDR4@3600 MHz | Asus RTX 4080 Super TUF | Corsair RM850e | Fractal Design Define S

Visa signatur

Care About Your Craft: Why spend your life developing software unless you care about doing it well? - The Pragmatic Programmer

Visa signatur

Main: 5800X3D | Arctic Freezer III 360 | ROG STRIX B550-I | 32 GB DDR4@3600 MHz | Asus RTX 4080 Super TUF | Corsair RM850e | Fractal Design Define S

Senast redigerat

Visa signatur

Care About Your Craft: Why spend your life developing software unless you care about doing it well? - The Pragmatic Programmer

Senast redigerat

Visa signatur

Care About Your Craft: Why spend your life developing software unless you care about doing it well? - The Pragmatic Programmer