CPU: R7 5800X3D | GPU: XFX 6900XT Merc 319 | MB: Gigabyte X570 PRO-I| RAM: 2x16 Corsair LPX@3600MHz CL18|Cooling: Scythe Ninja 5 (Noctua A12x25)|PSU: Corsair SF750|SSD: Samsung 970 EVO Plus 1TB + Corsair MP510 4TB + Samsung 850 EVO 2TB + Samsung 850 PRO 2TB|CASE:NR200P

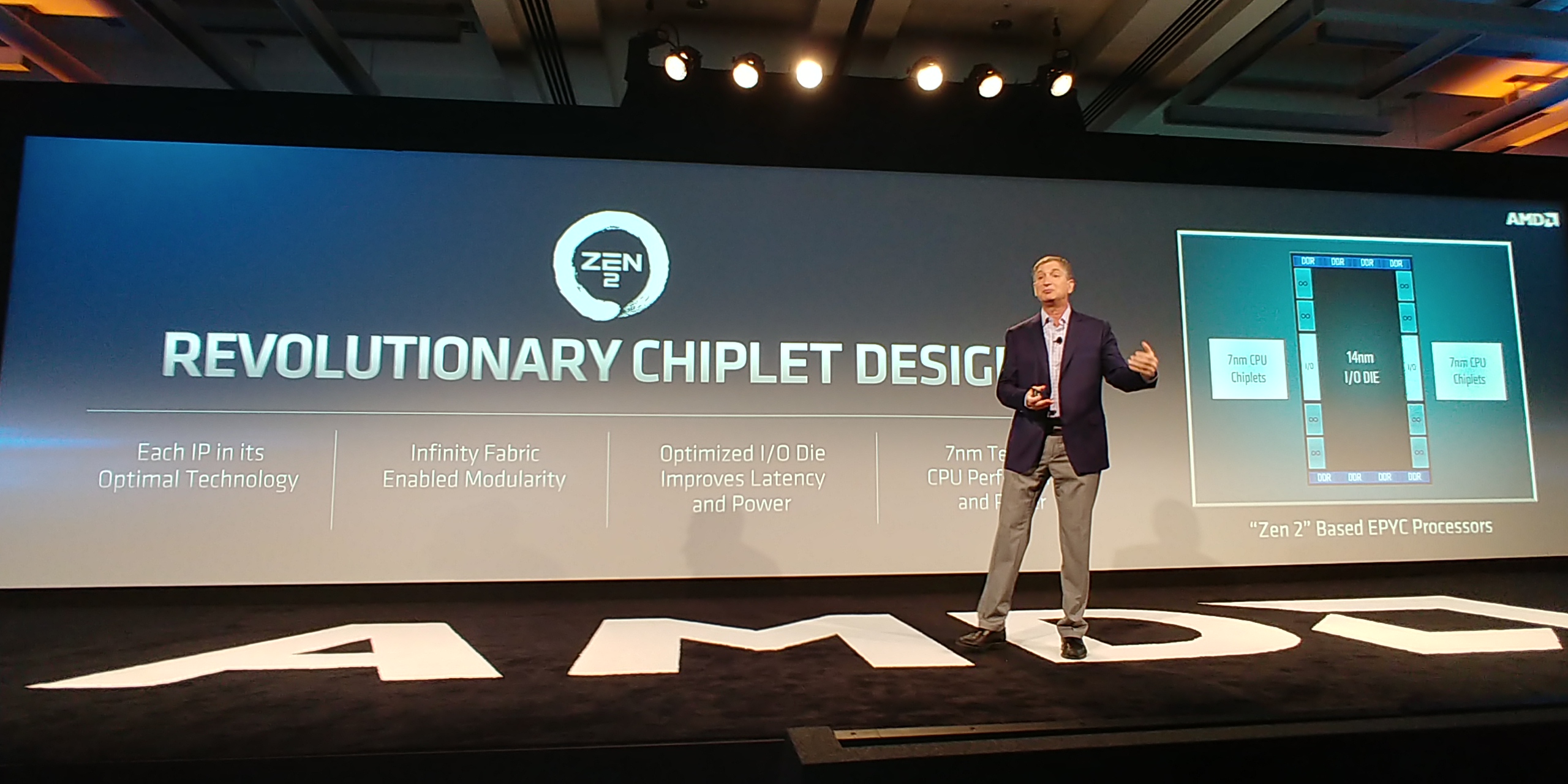

AMD avslöjar fler detaljer om arkitekturen Zen 2 på 7 nanometer

Visa signatur

Visa signatur

Asus Sabertooth X58 - Xeon X5680 - 12GB DDR3 - ASUS GTX1080 8GB

Visa signatur

🖥️ AMD Ryzen 3700x, MSI B350 Mortar Arctic, Corsair lpx 3200, Sapphire 6900XT Nitro, Mbpro 15, MacMini.

Visa signatur

Fractal Design Meshify 2 Compact w/ Dark Tint | Intel i5 12600K | Asus ROG Strix B660-F | 32 GB Corsair DDR5 5600 MHz CL36 | MSI Geforce RTX 3060 TI Ventus 2X OCV1 | 512 GB Samsung Pro 850 SSD + 2TB WD Black SN850 NVME PCI-E 4.0 | Corsair RM750X |

Visa signatur

🖥️ AMD Ryzen 3700x, MSI B350 Mortar Arctic, Corsair lpx 3200, Sapphire 6900XT Nitro, Mbpro 15, MacMini.

Visa signatur

Asus Sabertooth X58 - Xeon X5680 - 12GB DDR3 - ASUS GTX1080 8GB

Visa signatur

Citera för svar!

Visa signatur

🖥️ AMD Ryzen 3700x, MSI B350 Mortar Arctic, Corsair lpx 3200, Sapphire 6900XT Nitro, Mbpro 15, MacMini.

Visa signatur

Fractal Design Meshify 2 Compact w/ Dark Tint | Intel i5 12600K | Asus ROG Strix B660-F | 32 GB Corsair DDR5 5600 MHz CL36 | MSI Geforce RTX 3060 TI Ventus 2X OCV1 | 512 GB Samsung Pro 850 SSD + 2TB WD Black SN850 NVME PCI-E 4.0 | Corsair RM750X |

Visa signatur

Ryzen 7 3800X, Asus Prime X370 Pro, 32 GB LPX 3600, Gainward RTX 3060 Ti Ghost, 7 TB SSD + 4 TB HDD

Visa signatur

ozzed.net Min egenkomponerade 8-bit musik. Gillar du musiken från gamla klassiska NES eller Gameboy och liknande är det värt ett besök. :) Jag finns också på Spotify, Bandcamp, Jamendo, Youtube, och du kan även följa mig på Twitter och Facebook.

Vet du att du har fel? Signalera detta tydligt med Argumentationsfel och gärna Whataboutism.

Visa signatur

Fractal Design Meshify 2 Compact w/ Dark Tint | Intel i5 12600K | Asus ROG Strix B660-F | 32 GB Corsair DDR5 5600 MHz CL36 | MSI Geforce RTX 3060 TI Ventus 2X OCV1 | 512 GB Samsung Pro 850 SSD + 2TB WD Black SN850 NVME PCI-E 4.0 | Corsair RM750X |

Visa signatur

ozzed.net Min egenkomponerade 8-bit musik. Gillar du musiken från gamla klassiska NES eller Gameboy och liknande är det värt ett besök. :) Jag finns också på Spotify, Bandcamp, Jamendo, Youtube, och du kan även följa mig på Twitter och Facebook.

Vet du att du har fel? Signalera detta tydligt med Argumentationsfel och gärna Whataboutism.

Visa signatur

Care About Your Craft: Why spend your life developing software unless you care about doing it well? - The Pragmatic Programmer

Visa signatur

5900X | 6700XT

Visa signatur

Kids, always eat your vegetables and ALWAYS check run as administrator.

Visa signatur

Huvudriggen är en Gigabyte Aorus Xtreme | 128gb DDR5 6000 | Ryzen 7950X | 3080Ti

Utöver det är det för många datorer, boxar och servar för att lista :P

Visa signatur

Care About Your Craft: Why spend your life developing software unless you care about doing it well? - The Pragmatic Programmer

Visa signatur

3900X | Asus C8H | Trident Z 3800 | 6800 XT | MP600 | HX1000i | Core P5 | EK-WB

Visa signatur

Regn är snö på sommarn.