Tvivlar stark på att Alder Lake U kommer rå på ens första generationen Apple M CPUer, men finns tyvärr lägen där man är tvingad att köra x86 och tror Alder Lake U kommer bli riktigt bra, framförallt för modeller riktade mot ultratunna.

Finns självklart positiva delar i att Intel och AMD tävlar med varandra, men en uppenbar baksida är att (trots vad Intel säger om benchmarks) så har konkurrensen dessa två emellan resulterat i löjlig effekt hos deras "15 W" och "25-28 W" modeller. Både Intels och AMDs U-modeller drar ~2 gånger mer än deras märkning, Notebook check har uppmätt ~50 W för Intel 1165G7 och AMD 4800U (TDP är 28 W resp. 25 W) medan modeller som Intel 10850H och 4800H (både med 45 W TDP) uppmätts till 80-90 W.

Problemet är att <30 W kombinerat med high-end x86 betyder endera att man maximalt kan trycka in 4 kärnor, helst inte fler än 2 st alt. så får man acceptera klockfrekvenser på 2-3 GHz (trots 50 W effekt är frekvensen hos 25-28 W 2,2-3,5 GHz lite beroende på om det är 4,6 eller 8 kärnor).

Man kan ställa sig frågan hur lämpligt det är att köra "tunga" saker på tunna bärbara, fast finns fall där man av olika skäl ändå behöver göra detta. Att enbart ha en trave prestanda/W optimerade kärnor ger högsta möjliga absolut kapacitet, problemet med en sådan design är att det blir en kass design för interaktiva applikationer då sådan optimering ger dålig enkeltrådprestanda.

2-4 "stora" kärnor och 8 "små" kärnor gör det mest optimala av situationen om man vill verkligen hålla sig till 15-30 W, det även i praktiken. Det är inte heller speciellt svårt att skriva en schemaläggare som fungerar optimalt i >90 % av fallen: så länge det finns minst en "stor" kärna där ingen CPU-tråd är lastad så lägger man jobb där, sedan läggs jobbet på de "små" kärnorna och slutligen läggs det på "andra" tråden hos de "stora" kärnorna.

Apple kör stenhårt med den policyn i MacOS på M1, fungerar klockrent!

Lite svårt att se hur Microsoft ska kunna misslyckas med detta, framförallt då man fixar en betydligt mer komplicerad policy på Ryzen CPUer: I första hand läggs jobb på "bästa" CCX och man håller sig inom ett CCX så länge det finns minst en CPU-kärna där ingen CPU-tråd är lastad, sedan går man till näst bästa CCX etc. När alla CPU-kärnor har en CPU-tråd lastad börjar man om och lägger jobb på "andra" tråden. Kör man Ryzen master och har ett program där man kan exakt kontrollera hur många CPU-trådar som används ser man hur slaviskt denna policy hålls.

Sen kan det ändå krävas lite finjustering och i slutändan beror säkert på vad man optimerar för vad som blir bäst. T.ex. så skiljer sig Windows och Linux i hur de schemalägger på Ryzen, båda modellerna har för- och nackdelar. Linux prioriterar att utnyttja cache i så stor utsträckning som möjligt, så tvärtemot Windows sprider man maximalt över CCX!

Antag en 3900X (4 CCX med 3 kärnor och 6 trådar i varje). Om t.ex. 6 trådar används kommer man se att

Windows: två CCX har tre kärnor var lastade, en CPU-tråd per kärna

Linux: alla fyra CCX används (då de har L3$ som är bundet till CCX), två CCX har två kärnor aktiva och två har en kärna aktiv.

Finns ett par varianter för Alder Lake, men där känns det som om en är bäst för en förkrossande majoritet av fallen. Det är att först använda en tråd på varje stor kärna, sedan använda de små kärnorna (som saknar SMT) och sist lasta "andra" tråden på de stora kärnorna. Gissar att vi kommer se det både på Windows och Linux.

Så frågetecken för mig är inte om man kan fixa OS-schemaläggning. Stora frågetecknet är i stället hur pass mycket högre prestanda/W Gracemont faktiskt kan få jämfört med Golden Cove. Tror tyvärr det blir lite patetiskt jämfört med den brutala effektiviteten Icestorm kärnorna har i M1, de är å andra sidan de mest energieffektiva CPU-kärnor man hittar i någon mobil/dator just nu. För Alder Lake måste ändå Gracemont vara märkbart mycket perf/W effektivare än Goldmont, annars blir designen lite poänglös...

Vi lär i alla fall få se Alder Lake U med 15 W som kanske håller sig hyfsat nära 15 W tack vare bara 2 "stora" kärnor. Atom har än så länge inte haft problem med löjligt hög peak-effekt, varför skulle det ändras med Gracemont?

Fast hur är det mer komplicerat jämfört med att stationära modeller har väldigt länge haft andra antal kärnor än bärbara?

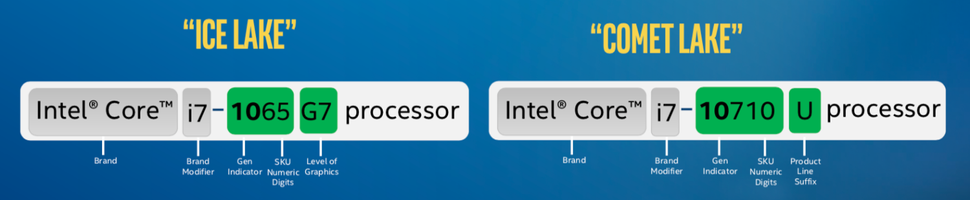

Det är en matris där en dimension är typ av produkt: fläktlös, ultratunn, släpbar/"gaming" etc. Inom varje produkttyp finns Pentium, i3, i5, i7 och i vissa segment i9. Inom varje segment avgör då t.ex. i7 var i prestandaskalan modellen står.