Vet inte vad jag antagit om Intels 10 nm process mer än vad som står listat på Chip Wiki. D.v.s. den var initialt förväntad att ge högre densitet jämfört med TSMC 7 nm, men problemet där var kravet på >= fyra litografisteg (pratades ju om upp till 6 st i vissa fall). Av allt att döma är ju "fixen" att man backat tillbaka till att matcha 7 nm TSMC i densitet vilket då aldrig kräver med än fyra litografisteg som värst.

Lite därför tror jag att sett till att TSMC nu är 1 år före här, och planerar redan delvis EUV när Intel fortfarande försöker optimera vidare sin befintliga. Som jag förstått den 7nm+ så kommer de inte satsa på prestanda, utan på att just öka densiteten på de delar som inte är så känsliga. Man kör en EUV "test fas" mao.

Så jag har ingen anledning att tro Intel magiskt kan ro hem någon mer "prisvärd" nod, då utvecklingen av denna 10nm lär ha kostat 4-5x vad den ursprungligen planerades. Pengar de behöver tjäna in också...

Sen är alla Wiki siter... inte alltid 100% pålitliga, speciellt inte när tex Intel blånekade något problem hela vägen tills de inte kunde längre. Trovärdigheten på deras planer imho är på nivå av Bill Clinton just nu... Och kan du inte lita på PR från tillverkaren, är det väldigt svårt att lita på en oberoende, obekräftad källa också. Man måste mao har lite... kritiskt tänkande till vad som påstås.

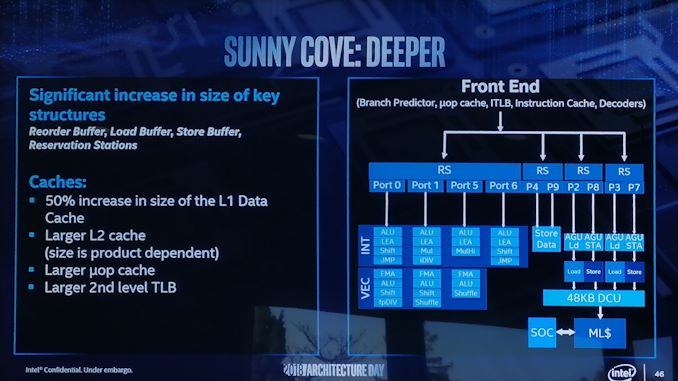

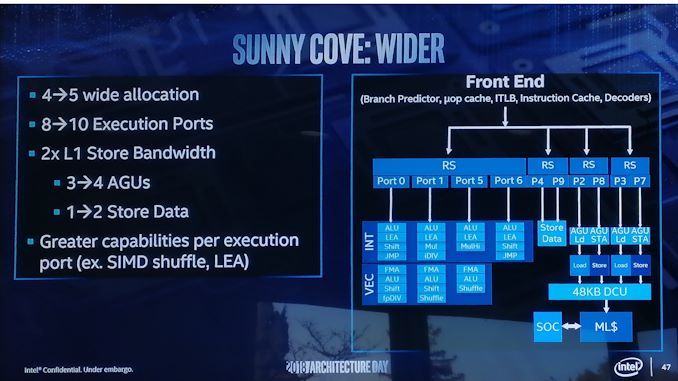

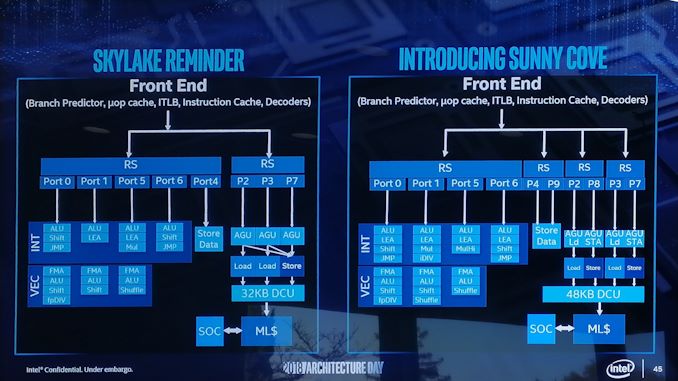

Har aldrig förväntat mig något annat än att frekvensen kommer gå ner jämfört med vad de idag har på 14 nm++, de har väl själva sagt att det är först med 10 nm++ (Willow Cove planerad 2020) som de förvänta sig matcha dagens frekvenser. Givet att läckta prestandasiffror på Sunny Cove pekar att IPC kommer öka 15-25 % finns ju lite spelrum.

De prestandaresultat som läckt för Zen2 pekar ju på mer eller mindre oförändrad IPC för heltalsberäkningar samt ~15 % högre IPC för flyttalsberäkningar samt upp mot 100 % för AVX. Så konsument produkterna baserade på Zen2 måste klocka klart högre jämfört med dagens Zen+, annars blir det bara fler kärnor (som de flesta desktop-applikationer ändå inte kan utnyttja).

Jag antar då det är 10nm++ "den nya", för den gamla 10nm++ var ju den som "lanserades 2018".

Ang Zen 2, helt förvånad är jag inte, då de inte kan göra en helt omdesignad CPU, utan bara en optimerad baserad på befintlig. Jag har också sett lite av dessa läckor och är lika besviken, men vill inte dra slutsatser om något förrän slutprodukten är på plats.

Har mycket svårt o se 15-25% ökning utom i specifika fall, då om det funnits den marginalen tidigare, hade Intel lätt tagit en del av den redan med Skylake vs tidigare. Sen är ju en fråga hur mycket dyrare chippet blir med den extra cache man trycker till där med.

Det jag kan tänka mig dock är att man tittat på optimering av mjukvaru-lappningarna för säkerhetshålen, om i sin tur säkert kan ge tillbaka en del av den kraften man tappat idag, vs pre patch. Men även det är bara 25% i väldigt specifika fall.

Och när 2020 kommer så har vi Zen3 att jämföra med, så det känns lite fel att anta något så exakt om en nod Intel inte har gjort klart, och en kärna de inte gjort klart, speciellt när nya säkerhetshål poppar upp, som kan tvinga förändringar vi inte sett.

Just Skylake ver 6 kommer ju inte erbjuda några förbättringar, mer än 2 kärnor till... och det är dessa Zen2 ska konkurrera mot 14nm++ vs 7nm.

Sedan undrar jag lite vad du baserar dina ekonomiska antagande på kring kostnader av kretsar. Intel har trots vad du anser vara "framstressade och lappade kretsar" 50 % högre bruttomarginal, det är ju direkt kostnad för tillverkning dividerat med omsättning (d.v.s. exklusive kostnad för FoU, administrativa uppgifter och liknande).

Får inte heller ihop hur en krets som i7-9700K inte skulle vara väldigt lönsam. Om man antar att Zen+ och Coffe Lake R tillverkas på ungefär lika mogna noder (d.v.s. väldigt mogna noder med väldigt låg D0) idag är tillverkningskostnaden för en 213 mm² krets ~20 % högre jämfört med en 179 mm² krets. Och numera går väl kretsen som används till 9900K ända ner till i5-9400 (plus att H-serien och S-serien är väl ändå samma krets, så kretsen används även för high-performance bärbara)?

Och de har också 2x priset på CPUn. Tror du verkligen de hade haft samma vinst om de halverat priset?

Eller hur tror du AMDs bruttomarginal hade sett ut om de kunde sälja 2600X till 9700ks pris?

Som sagt tidigare, de lever på folks troende att 5fps är något de får mer, från extrem benchmarks, med deras 1060 GPU och 2400 DDR4...

AMD just nu dumpar priset, för att köpa marknadsandelar, något du kan se i de flesta segment och ändå får vinst, även om de är inte markant stora i alla. Faktum att OEM har börjat få upp ögonen är en stor sak dock. Skulle AMD kunna släppa en konkurrenskraftig CPU till nu under 2019, så lär de plocka mer marknad och kan sälja en dyrare CPU, för mer vinst, vilket gör just en CPU som 9700k inte direkt vinst-vänlig, och Intel hoppas väl att 10/10 trådad variant ska "lösa problemet"...

Ang om den används i bärbara vågar jag inte svara på. Det skulle inte förvåna mig, för de behöver som sagt sälja dem. Men du antog precis innan att AMD inte kan göra en prisvärd bärbar lösning, så... om nu AMD kan släppa något som konkurrera även där, vs bärbara H CPUer... lär Intel ha svårare med dessa också.

Egentligen enda jag ville belysa är att chiplets har absolut fördelar sett till kostnad, men dessa fördelar gäller egentligen bara på serversidan för tillfället.

Jag vill inte hålla med, då det beror på om du räknar totala RND + tillverkning + storlek av marknaden och vad du kan sälja från denna produkt. Om du kan sälja en produkt för 2x priset som din konkurrent, har du verkligen en fördel till kostnad, eller är det pga andra bitar? Om du har högre kostnad, men kan göra mer med den, är det verkligen dyrare, om du får in pengarna från fler håll istället?

Kan förstå ditt tänk med chiplet i prestanda-biten, men som sagt, du har redan en annan I/O i desktop än server, och du antar att den är "den enda". Inget som säger att AMD inte kan välja o vraka i den tillverkningen, eller göra mindre I/O nästa år när 7nm mognat mer och chiplets kan gå till 7nm+ tex. Eller sätta en mer kompetent I/O med stackat HBM och en iGPU kraftfull nog att konkurrera med en hel del dGPUer. Intel kan inte göra denna optimering, eller flexibilitet, och det för att även om produkten kanske "just nu" kostar mer på papper, kan du får mer ur tillverkningen i slutprodukten.